Partneři Projektu CAD

| Po | Út | St | Čt | Pá | So | Ne |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | ||||

| 4 | 5 | 6 | 7 | 8 | 9 | 10 |

| 11 | 12 | 13 | 14 | 15 | 16 | 17 |

| 18 | 19 | 20 | 21 | 22 | 23 | 24 |

| 25 | 26 | 27 | 28 | 29 | 30 | 31 |

- 19.05. Unreal Engine – vizualizace

- 21.05. AutoCAD – kurz pro pokročilé

- 21.05. Autodesk Maya – pokročilé techniky renderování

- 25.05. AutoCAD – kurz pro středně pokročilé

- 25.05. Blender – pokročilé materiály a renderování

- 26.05. Webinář: Revolutionizing CAE with meshless simulation

- 27.05. Autodesk Fusion 360 – základní kurz (úvod do parametrického modelování)

- 27.05. Školení pro metrology - Nejistoty měření

- 28.05. workshop Strukturální mechanika v programu COMSOL Multiphysics

- 29.05. Autodesk Fusion 360 – pro uživatele Autodesk Inventor

Aktuální články

- Nová autonomní elektroformule týmu EFORCE Prague Formula

- Epson SureColor SC‑F20000 zvyšuje produktivitu průmyslové sublimace barvivem

- Realizujeme projekty na škole s využitím 3D tisku, 12. díl

- Početná skupina vystavovatelů na Make-to-Order Days

- Lumion 2026 - Novinky souhrnně

- Dell Pro 5 Micro: Copilot+ PC připojí až pět monitorů

- Odolná mobilita s tabletem G140 Copilot+ a technologií AMD

- Odborný seminář MCAE – 3D tisk pro výrobu

Evropa zahajuje projekt DARE SGA1 |

| Pondělí, 17 Březen 2025 16:31 | |

|

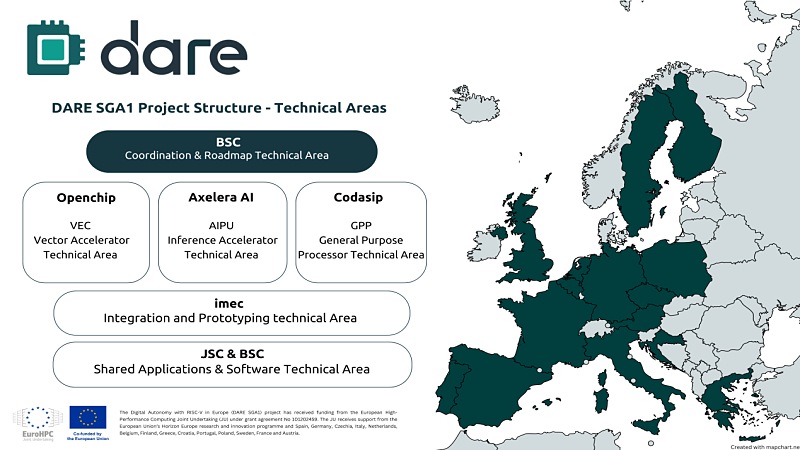

Sdružuje 38 předních partnerů z celé Evropy s cílem vyvinout evropské procesory a výpočetní systémy nové generace, včetně optimalizovaného softwarového ekosystému, určeného pro výzkumné a průmyslové aplikace. Tato ambiciózní iniciativa podpoří inovace v oblasti hardwarových i softwarových technologií a využije plnou sílu HPC a AI k vývoji bezpečných, efektivních a evropsky orientovaných řešení pro budoucnost. Řešení deficitu digitální autonomieEvropa je podle vedoucích projektu dlouhodobě závislá na mimoevropských HW a SW řešeních pro svou superpočítačovou infrastrukturu. Tato závislost podle odborníků ohrožuje bezpečnost, ekonomickou stabilitu a technologickou konkurenceschopnost. DARE SGA1 se snaží tento trend zvrátit využitím otevřeného ekosystému RISC-V a nejnovější technologie čipletů (chiplet lze popsat jako diskrétní polovodičovou součástku pečlivě navrženou tak, aby plnila specifickou funkci v systému integrovaných obvodů) a vytvořením evropských produktů, které budou pohánět budoucí evropské superpočítače. Kliknutím sem uvidíte mapu projektu v plné velikosti. Klíčové technologické inovaceJádrem projektu DARE SGA1 je vývoj tří čipletů na bázi RISC-V, z nichž každý plní určitou úlohu ve výpočtech HPC a AI:

Tyto čiplety budou vyvinuty a vyrobeny v moderních technologických CMOS uzlech. DARE SGA1 využívá přístup společného návrhu HW/SW, přičemž k řízení vývoje využívá sadu evropských aplikací HPC a AI. Souběžně s návrhem HW bude vytvořen kompletní SW zásobník optimalizovaný pro HW DARE SGA1, přičemž bude využit včasný přístup k emulaci a simulaci HW RISC-V. Kromě toho bude DARE zahrnovat průzkumné činnosti pro návrh SW a HW pro nejbližší budoucnost a plánovací činnosti pro provádění studií škálovatelnosti pro budoucí nasazení superpočítačů. Evropská spolupráceKromě již zmíněných společností Openchip, Axelera AI a Codasip budou technickými vedoucími společnost imec a Jülich Supercomputing Centre (JSC) při Forschungszentrum Jülich. Kromě toho, že BSC bude celkovým koordinátorem, povede také roadmapping a také úsilí o nalezení cesty k VEC. Plán pro budoucnost evropského HPCDo konce své první fáze položí DARE SGA1 základy pro první plně evropský systém HPC, který podpoří technologickou soběstačnost a zajistí, aby evropský průmysl, výzkum a celá společnost mohly využívat bezpečná, vysoce výkonná a energeticky účinná výpočetní řešení. Cílem projektu DARE SGA1 je definovat plán pro evropské post-exascale superpočítače. Projekt připraví půdu pro budoucí generace superpočítačů, které budou navrženy, postaveny a optimalizovány v Evropě, a zajistí, že Evropa zůstane na špici ve vývoji a využívání HPC a AI. O projektu DAREDigitální autonomie s RISC-V v Evropě (DARE SGA1) je rozsáhlý evropský superpočítačový projekt, který získal finanční prostředky od společného podniku pro vysoce výkonnou výpočetní techniku (JU) na základě grantové dohody č. 101202459. Cílem projektu DARE SGA1 je vyvinout prototypy systémů HPC a umělé inteligence založené na čipech navržených a vyvinutých v EU podle průmyslových standardů.

Mohlo by vás zajímat:

|

Projekt Digital Autonomy with RISC-V in Europe, Special Grant Agreement 1 (DARE SGA1) oficiálně zahajuje první fázi iniciativy, jejímž cílem je zvýšit technologický pokrok Evropy v oblasti vysoce výkonných počítačů (HPC) a umělé inteligence (AI). Projekt DARE SGA1 je podporovaný

Projekt Digital Autonomy with RISC-V in Europe, Special Grant Agreement 1 (DARE SGA1) oficiálně zahajuje první fázi iniciativy, jejímž cílem je zvýšit technologický pokrok Evropy v oblasti vysoce výkonných počítačů (HPC) a umělé inteligence (AI). Projekt DARE SGA1 je podporovaný