Partneři Projektu CAD

HDL Verifier automaticky generuje UVM komponenty |

| Autor článku: MathWorks | |

|

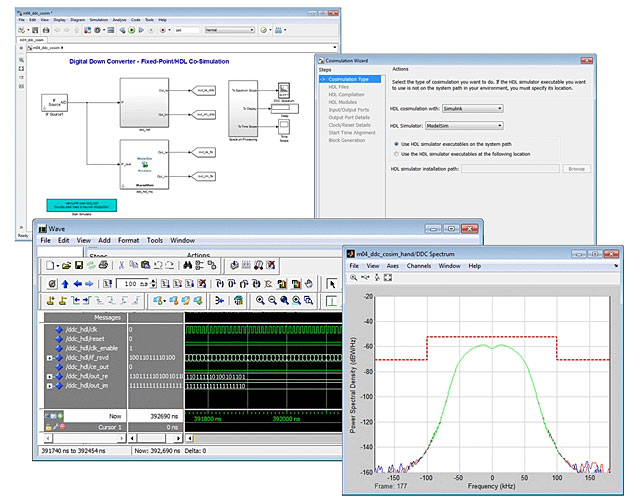

Vývojáři algoritmů a architekti systémů obvykle vyvíjejí nový obsah algoritmů v Matlabu a Simulinku. Pro ověřování návrhu (Design Verification – DV) poté inženýři používají modely Matlabu a Simulinku jako referenční, neboť manuálně zadávají kód pro zkušební testy RTL, což může být velmi časově náročný proces. Nyní s HDL Verifierem mohou DV inženýři automaticky generovat komponenty UVM, jako jsou sekvence nebo výsledkové tabulky, z modelů na úrovni systému, které již byly vyvinuty v Simulinku. Tento přístup zkracuje čas, který inženýři stráví vývojem zkušebních testů pro návrhy obvodů ASIC a FPGA používaných v aplikacích, jako je bezdrátová komunikace, vestavěné vidění a ovládací prvky.

Díky novým funkcím nyní HDL Verifier nabízí rozšířenou podporu týmům pro ověřování návrhu odpovědných za ověřování tvorby obvodů ASIC a FPGA. Úkolováni vývojem přísných zkušebních testů v HDL simulátorech pomocí manuálního zadávání kódu v SystemVerilogu, mohou nyní tyto týmy pro ověřování návrhu generovat ověřovací komponenty přímo z existujících modelů Matlabu a Simulinku a opětovně je používat k urychlení vytváření prostředí pro ověřování výroby.

Mohlo by vás zajímat:

|

Společnost

Společnost