Partneři Projektu CAD

| Po | Út | St | Čt | Pá | So | Ne |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

| 29 | 30 | 31 |

- 08.04. Školení pro metrology - Měření drsnosti povrchu

- 09.04. Školení pro metrology - Měření tvrdosti kovových materiálů

- 10.04. Trimble SketchUp – workshop dynamické komponenty

- 10.04. Trimble SketchUp – workshop práce s terénem

- 10.04. Webinář: Synchronizace týmů a zefektivnění procesů v CATIA

- 13.04. AutoCAD – kurz pro středně pokročilé

- 13.04. Blender – sculpting a tvorba komplexních modelů

- 15.04. Školení pro metrology - Měření drsnosti podle nových norem

- 16.04. workshop Strukturální mechanika v programu COMSOL Multiphysics

- 17.04. Webinář: DELMIA Augmented Experience

Aktuální články

- Firmy se bojí zaspat, robotizaci si pořizují s předstihem

- Poslední volná místa na Designcenter NX User Event

- Prezentujeme studentské projekty pomocí virtuální reality

- Zákaznické dny TAJMAC-ZPS 2026

- Data ze stavby nekončí kolaudací

- Sygic GPS Navigation s otestovaným Motorbike Modem

- Stavba mrakodrapu pomocí BIM: Šanghajská věž

- Novinky programu NBL Landscape Designer 2026 CZ

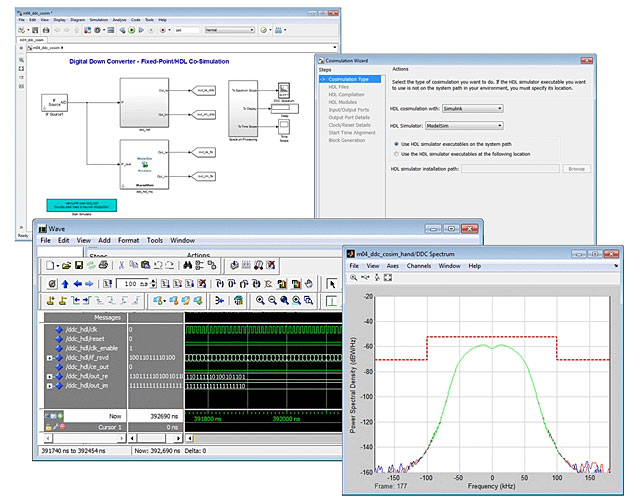

HDL Verifier automaticky generuje UVM komponenty |

| Čtvrtek, 16 Leden 2020 14:06 | |

|

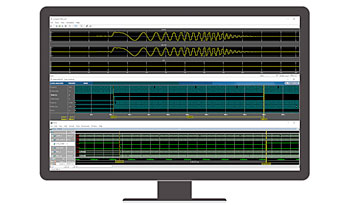

Vývojáři algoritmů a architekti systémů obvykle vyvíjejí nový obsah algoritmů v Matlabu a Simulinku. Pro ověřování návrhu (Design Verification – DV) poté inženýři používají modely Matlabu a Simulinku jako referenční, neboť manuálně zadávají kód pro zkušební testy RTL, což může být velmi časově náročný proces. Nyní s HDL Verifierem mohou DV inženýři automaticky generovat komponenty UVM, jako jsou sekvence nebo výsledkové tabulky, z modelů na úrovni systému, které již byly vyvinuty v Simulinku. Tento přístup zkracuje čas, který inženýři stráví vývojem zkušebních testů pro návrhy obvodů ASIC a FPGA používaných v aplikacích, jako je bezdrátová komunikace, vestavěné vidění a ovládací prvky.

Díky novým funkcím nyní HDL Verifier nabízí rozšířenou podporu týmům pro ověřování návrhu odpovědných za ověřování tvorby obvodů ASIC a FPGA. Úkolováni vývojem přísných zkušebních testů v HDL simulátorech pomocí manuálního zadávání kódu v SystemVerilogu, mohou nyní tyto týmy pro ověřování návrhu generovat ověřovací komponenty přímo z existujících modelů Matlabu a Simulinku a opětovně je používat k urychlení vytváření prostředí pro ověřování výroby.

Mohlo by vás zajímat:

|

Společnost

Společnost