Partneři Projektu CAD

| Po | Út | St | Čt | Pá | So | Ne |

|---|---|---|---|---|---|---|

| 1 | ||||||

| 2 | 3 | 4 | 5 | 6 | 7 | 8 |

| 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| 16 | 17 | 18 | 19 | 20 | 21 | 22 |

| 23 | 24 | 25 | 26 | 27 | 28 | 29 |

| 30 |

- 09.06. Autodesk 3DS MAX – kurz

- 09.06. AutoCAD a AutoCAD LT – základní kurz

- 12.06. AutoCAD – kurz pro středně pokročilé

- 12.06. workshop Strukturální mechanika v programu COMSOL Multiphysics

- 16.06. Autodesk Inventor – kurz pro pokročilé (sestavy a strojní návrhy)

- 16.06. AutoCAD a AutoCAD LT – základní kurz

- 23.06. Unreal Engine – vizualizace

- 23.06. AutoCAD – kurz pro středně pokročilé

- 23.06. Unreal Engine – vizualizace

- 25.06. Autodesk Inventor – kurz pro pokročilé (sestavy a strojní návrhy)

Aktuální články

- Eurocom uvádí na trh pracovní stanici Nightsky RX515

- Virtuální realita při návrhu interiérů ve žďárské SPŠ

- UltiMaker S6: cenově dostupný, vysoce výkonný 3D tisk

- Corpis Maps s FLOWii – nový rozměr řízení byznysu

- Sympozium OPEN MIND Sales & Tech 2025

- Konference HERITAGE BIM 2025 a BIM DAY 2025

- Realizujeme projekty na škole s využitím 3D tisku, 7. díl

- Staňte se přednášejícím na BIM OPEN 2025 v Ostravě

HDL Verifier automaticky generuje UVM komponenty |

| Čtvrtek, 16 Leden 2020 14:06 | |

|

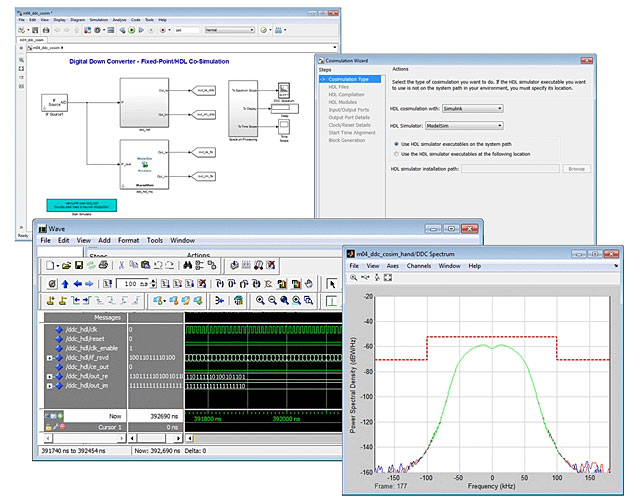

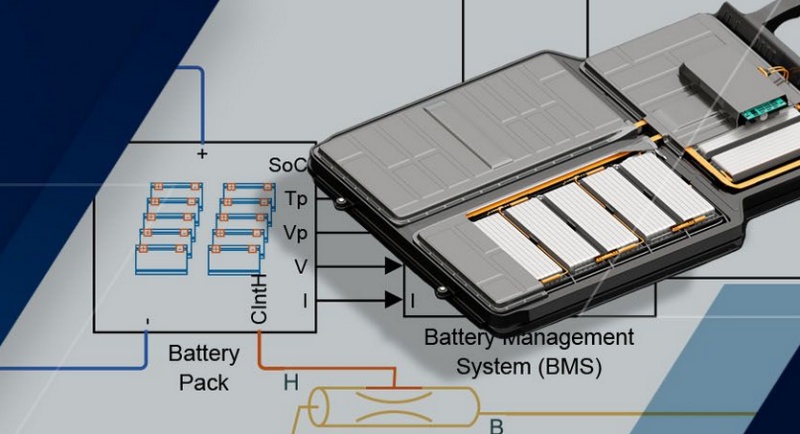

Vývojáři algoritmů a architekti systémů obvykle vyvíjejí nový obsah algoritmů v Matlabu a Simulinku. Pro ověřování návrhu (Design Verification – DV) poté inženýři používají modely Matlabu a Simulinku jako referenční, neboť manuálně zadávají kód pro zkušební testy RTL, což může být velmi časově náročný proces. Nyní s HDL Verifierem mohou DV inženýři automaticky generovat komponenty UVM, jako jsou sekvence nebo výsledkové tabulky, z modelů na úrovni systému, které již byly vyvinuty v Simulinku. Tento přístup zkracuje čas, který inženýři stráví vývojem zkušebních testů pro návrhy obvodů ASIC a FPGA používaných v aplikacích, jako je bezdrátová komunikace, vestavěné vidění a ovládací prvky.

Díky novým funkcím nyní HDL Verifier nabízí rozšířenou podporu týmům pro ověřování návrhu odpovědných za ověřování tvorby obvodů ASIC a FPGA. Úkolováni vývojem přísných zkušebních testů v HDL simulátorech pomocí manuálního zadávání kódu v SystemVerilogu, mohou nyní tyto týmy pro ověřování návrhu generovat ověřovací komponenty přímo z existujících modelů Matlabu a Simulinku a opětovně je používat k urychlení vytváření prostředí pro ověřování výroby.

Mohlo by vás zajímat:

|

Společnost

Společnost